新闻资讯

开关模式电源(开关电源)因其高效性和灵活性而广受欢迎。但它们也带来了挑战,因为其应用已经延伸到新的领域。最明显的是,其高频切换会对系统的其他部分产生电磁干扰 (EMI)。此外,导致 EMI 的因素同样也会降低效率,从而削弱开关电源关键的能效优势。

为了避免这些问题,设计人员在配置“热回路”(电源电路中发生快速开关的部分)时必须特别小心。将等效串联电阻 (ESR) 和等效串联电感 (ESL) 造成的热回路寄生损耗降至最低至关重要。这可以通过选择高度集成的电源元件和精心设计的印刷电路板(PC 板)布局来实现。

本文将介绍热回路和寄生损耗来源,具体包括耦合电容器、功率场效应晶体管 (FET) 和电路板过孔等。然后会展示 Analog Devices 的高集成度电源转换器实例,并介绍各种电路板布局及其对寄生参数的影响。最后还介绍了降低 ESR 和 ESL 的实用技巧。

开关电源热回路基本原理

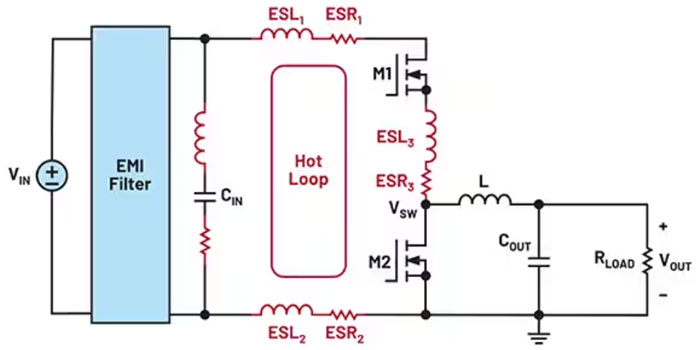

任何涉及快速开关电流的电源设计,如升压、降压升压和反激式转换器,都会出现高频开关电流热回路。这个概念可以通过一个简化的降压转换器来说明(图 1)。左侧的回路(红色)包含所有开关元件;电路产生的高频电流包含在其中,并形成热回路。

图 1:一个简化的降压转换器说明了热回路(红框)的原理。(图片来源:Analog Devices)

“热”是因为电路的这一区域进行着大量的能量转换和开关活动,而这些活动往往伴随着热量的产生。对这些热回路进行合理布局和设计对于最大限度地减少 EMI 和确保电源的高效运行至关重要。

图 2 中更为现实的电路是一个 DC-DC 同步降压转换器。在这个热回路中,物理元件(标为黑色)是输入电容器 (CIN) 和开关金属氧化物半导体场效应晶体管 (MOSFET)(M1 和 M2)。

图 2:真实世界的热回路不可避免地包含寄生参数(以红色显示)。

热回路中的寄生参数用红色标出。ESL 通常在纳亨 (nH) 范围内,而 ESR 则在毫欧 (mΩ) 范围内。高频开关会导致 ESL 内产生瞬时振荡,从而产生电磁干扰。储存在 ESL 中的能量会被 ESR 消散,从而导致功率损耗。

利用集成元件可将寄生参数降至最低

这些寄生阻抗(ESR、ESL)会出现在元件内部和热回路电路板印制线上。为了尽量减少这些参数,设计人员必须仔细选择元件并优化电路板布局。

实现这两个目标的方法之一就是使用集成元件。这些集成元件消除了连接分立元件所需的电路板印制线,同时减少了热回路的总面积。两者都有助于减少寄生阻抗。

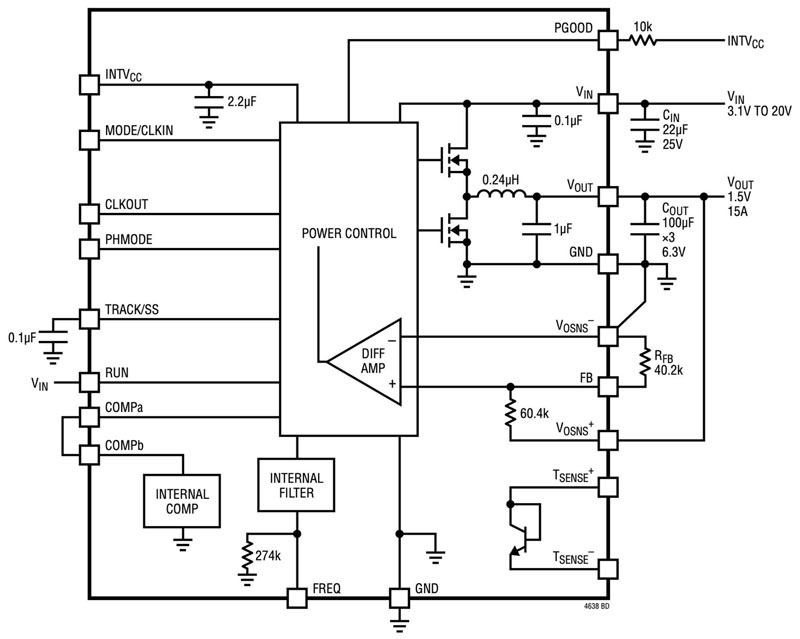

Analog Devices 的 LTM4638 降压型 µModule 稳压器就是高集成度元件的一个极佳实例。如图 3 所示,这款 15 安培 (A) 开关稳压器集成了开关控制器、功率 FET、电感器和支持元件,全部封装在一个 6.25 × 6.25 × 5.02 毫米的微型封装内。

图 3:LTM4638 µModule 稳压器集成了降压转换器所需的许多元件。

LTM4638 还具有其他几项功能,可减少寄生损耗。具体包括:

· 快速瞬态响应:这可以使稳压器根据负载或输入的变化快速调整输出电压,并通过快速过渡到次优工作状态,最大限度地缩短寄生损耗的持续时间并降低其影响。

· 断续模式运行:这允许电感器电流在下一个开关周期开始前降至零。这种模式通常在轻负载条件下使用,通过在部分周期内使电感器断电,从而减少电感器的开关和铁损。

· 输出电压跟踪:这能够让转换器输出跟踪参考输入电压。该功能通过精确控制输出电压的升降,降低了可能加剧寄生损耗的过冲或欠冲的可能性。

通过元件布局将寄生参数降至最低

使用 LTM4638 构建同步降压转换器需要分别添加散装的输入和输出电容器 CIN 和 COUT。这些电容器的位置选择会对寄生参数产生重大影响。

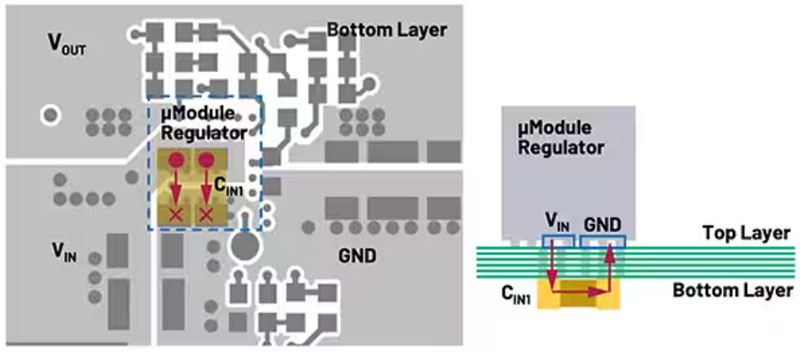

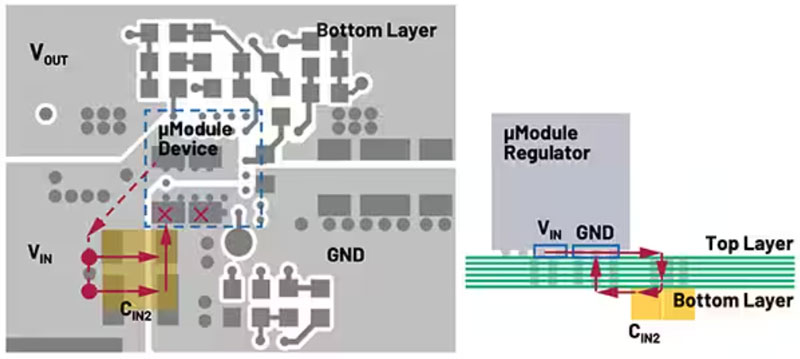

Analog Devices 使用针对 LTM4638 的 DC2665A-B 评估板进行的实验说明了 CIN 位置选择的影响。后来,DC2665B-B 取代了该评估板,但原理仍适用。图 4 至图 6 展示了 CIN 的三种不同布局和相应的热回路。垂直热回路 1(图 4)和 2(图 5)分别将 CIN 放在底层稳压器的正下方或侧面。水平热回路(图 6)将电容器置于顶层。

图 4:垂直热回路 1 底视图和侧视图。CIN 位于稳压器正下方,通过过孔连接。

图 5:垂直热回路 2 底视图和侧视图。CIN 位于稳压器下方,但在稳压器旁边,需要电路板印制线和过孔。

图 6:水平热回路俯视图和侧视图。CIN 位于顶层,通过印制线与稳压器相连。

垂直热回路 1 的路径最短,可避免使用电路板印制线。因此,预计它的寄生参数最低。使用 FastHenry 以 600 kHz 和 200 兆赫兹 (MHz) 的频率分析每个热回路,结果显示情况确实如此(图 7)。

图 7:不出所料,最短路径的寄生阻抗最低。

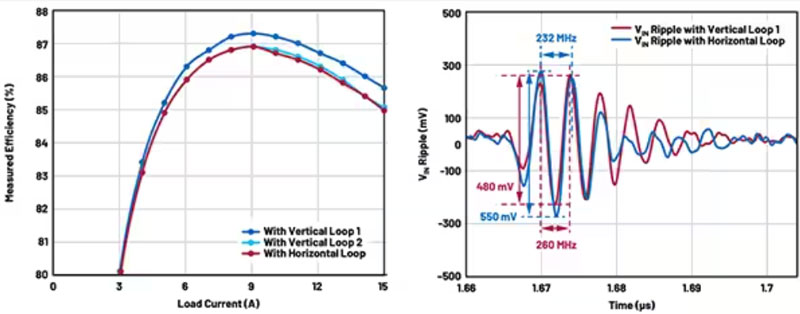

虽然我们无法直接测量这些寄生参数,但可以预测和测试它们的影响。具体来说,ESR 越低,效率越高,ESL 越低,纹波越小。实验验证证实了这些预测,垂直热回路 1 在这两项指标上都有更好的表现(图 8)。

图 8:实验结果证实,垂直热回路 1 实现了更好的效率和纹波。

最小化分立元件的寄生参数

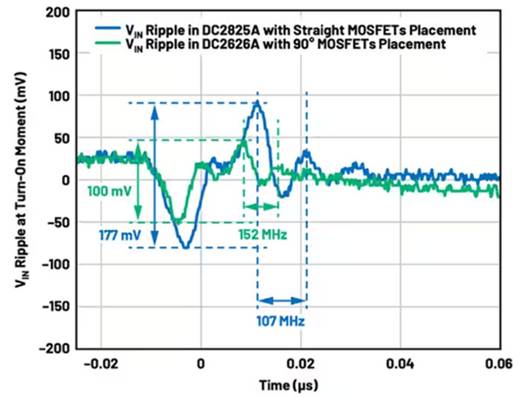

虽然集成器件具有许多优势,但某些开关电源仍需要分立元件。例如,大功率应用可能会超出集成设备的能力。在这种情况下,分立功率 FET 的位置和封装尺寸都会对热回路 ESR 和 ESL 产生重大影响。如图 9 所示,通过测试两块评估板可以看出这些影响,这两块评估板都采用了高效的 4 开关同步降压升压控制器:

· DC2825A 评估板基于 LT8390 降压升压稳压器。其 MOSFET 平行放置,方向相同。

· DC2626A 评估板基于 LT8392 降压升压稳压器。两对 MOSFET 成 90˚ 角放置。

图 9:DC2825A(左)将 MOSFET 平行放置,而 DC2626A(右)将 MOSFET 以 90˚ 角垂直放置。

这两块电路板使用相同的 MOSFET 和电容器进行测试,在 10 A 和 300 千赫兹 (kHz) 频率下进行 36 至 12 伏的降压操作。结果表明,90˚ 放置的电压纹波更低,谐振频率更高,表示由于热回路径更短,PC 板 ESL 更小(图 10)。

图 10:采用 90˚ MOSFET 布局的 DC2626A 具有更低的纹波和更高的谐振频率。

其他布局考虑因素

在热回路中采用顶部 FormVVia 布置也会影响回路 ESR 和 ESL。一般来说,增加过孔可以降低电路板的寄生阻抗。不过,这种减少与过孔数量并不成正比。过孔靠端子焊盘近一些可显著降低 ESR 和 ESL。因此,应在靠近关键元件(CIN 和 µModule 或 MOSFET)焊盘的地方放置多个过孔,以尽量减小热回路阻抗。

还有许多其他方法可以对电气和热性能产生积极影响。优化热回路的最佳做法包括:

· 在大电流通路(包括VIN、VOUT 和接地)上使用大面积的电路板铜,以尽量减少电路板传导损耗和热应力。

· 在单元下方放置专用的电源接地层。

· 在顶层和其他功率层之间使用多个过孔进行互连,以尽量减少传导损耗,并降低模块热应力。

· 不要将过孔直接放在焊盘上,除非对其进行封盖或电镀。

· 对于连接到信号引脚的组件,应使用独立的信号接地铜区,将信号接地连接到单元下方的主接地引脚。

· 在信号引脚上引入测试点进行监测。

· 保持时钟信号与频率输入印制线之间的距离,以尽量减少串扰造成噪声的可能性。

发布日期: 2023-12-04

发布日期: 2024-08-21

发布日期: 2024-05-29

发布日期: 2023-11-24

发布日期: 2024-06-17

发布日期: 2024-07-17

发布日期: 2025-02-11

发布日期: 2023-12-13

发布日期: 2026-04-03

发布日期: 2026-04-03

发布日期: 2026-04-03

发布日期: 2026-04-03

发布日期: 2026-03-31