在时钟频率越来越高的情况下,数字电路和接口的行为与模拟电路非常相似。 因此,为了确保新的和重新设计的解决方案中的接口质量,必须引入新的测量方法和测量设备。

当今车辆中的信息娱乐系统所需的功能只能通过新型高速显卡和超快内存来实现。 我们所有的数字社交信息都是由大型服务器记录和处理的,这些服务器需要快速从高功率存储中检索数据并将其传输到各种较低级别的系统进行处理。

连续拍摄大量图像并以高分辨率格式保存,并在各种情况下发送到AI服务器; 先进的算法可以快速处理数据并输出高质量的结果。

典型的人工智能服务器就像任何其他先进的计算机系统一样:它由主板和其他先进组件组成,例如显卡、硬盘驱动器和大量连接的交换机。 所有这些设备的连接标准均基于 PCI Express (PCIe)。 自 2003 年推出第一代以来,PCI-SIG 标准一直致力于实现每一代 PCIe 数据速率加倍的目标。

然而,处理更高的数据传输速率意味着电子系统的开发也需要一步步继续,这也需要大量的技巧和耐心。 由主板和附加卡组成的复杂且互连的系统需要仔细分解为更小的电路,每个子电路都作为下一阶段改进的目标,即使在整个电路设计完成之后也是如此。

随着带宽需求的增加,PCIe Gen4 已在各个市场取代了上一代技术。 为此,开发人员不断更新当前的电路设计,并交换有关布线和布线的建议和指南,以最大程度地减少串扰或解决因过孔放置不当引起的 EMI 问题。

这些开发人员通常是先驱者,他们仍然面临着确定潜在信号衰减可能发生在何处、为何发生以及存在多少冗余的问题。 简单地将插头更换为更实惠的插头,由于机械或供应链问题、固件或硬件升级或制造过程中的任何变化而在最后一刻调整引脚分配可能是一场噩梦,因为解决这些问题需要额外的努力 以及重新设计电路板的时间。

TMT4 PCIe性能综合测试仪

对主板应用 BIOS 更新可以实现与 NVMx SSD 驱动器的全速通信,但也可能会导致电气物理变化。 在固件升级期间,连接到主板并与CPU通信的开关和定时器的配置可能会改变,并且在改变之后执行“通道容限测试”可能会给出不同的测试结果。 抖动限制的改进可以随时发生,在确定对 PHY 物理层的实际影响之前,综合仿真工具中的准确建模是虚拟验证的关键。 然而,模拟并不总是代表真实情况,因此仍然必须执行物理级测试。

低功耗 Gen3 和 Gen4 配置经常被重新配置,以实现潜在的节能配置。 即使在微调电源电路时,您也应该确保重新供电步骤足够快,以满足连接建立时间要求,因为仅增加几毫秒就可能导致需要重新验证的新条件。

然而,在这些场景下,重新对线路设计进行验证可能并不经济高效:事实上,对在物联网/消费者应用中销售且依旧使用 PCIe Gen3 连接的非关键性低成本产品进行微小的设计变更后重新花费时间进行实验室验证可能并不合理。

半导体企业需要遵循复杂的决策路径,以便针对某设计变更根据经验作出是否进行新的验证的判断。判断的标准源于风险和成本分析。

在此情况下使用到的测试仪器通常为误码率测试仪 (BERT) 和示波器。这些仪器也在不断发展,以满足每一代 PCIe 标准的要求,但根据用户的经验,这些仪器的操作普遍比较有挑战性。

验证成本不仅仅与硬件的购置成本有关,而且与执行此工作而配备的专家资源的时间成本有关。一名软件操作助手可以通过测试来保证进行每项检测时被测设备都进行了正确的电气连接,但是使用 BERT 和带探头的示波器的整体过程还是需要一名专家全程进行监控。

以链路初始化为例,它是一个物理层的控制过程,其对于设备物理层的初始化和将一些设置应用至链路是不可或缺的。在正常操作中,这个过程是自动的,但如果您对深度的设计验证感兴趣,则需要对特定数据进行编码的软件来允许用户诊断和监控在状态转换期间信号发生的潜在问题。BERT 通常用于精确控制的链路训练和均衡,涵盖三个关键测试领域:合规性、容限测试和故障检测。此外还需要实时示波器,需要高度开发的应用软件在接收端自动完成复杂的测试过程,并与 BERT 实时通讯,交换配置参数数据。

容限测试还需要在 PCIe 插槽的每个通道上依次重复一系列固定的步骤,包括设置触发电压时间。这种涉及多种不同高度开发设备的冗长且复杂的工序可能引入人为失误,进而影响到整个检测程序的效率。

Tektronix 并非寻求 BERT/示波器系统的替代品或是已经广泛使用的 On Chip Lane Margining Tool,而是采取了不同的解决方案。

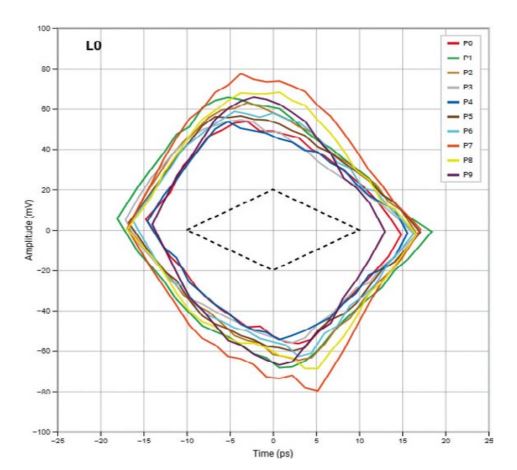

TMT4 PCIE性能综合测试仪为用户实时显示眼图。

TMT4 PCIE 综合性能测试仪开创了业界评估 PCIe Gen 3 和 PCIe Gen 4 链路运行状况的独特能力。

TMT4 PCIE 性能测试仪可连接到最流行的 PCI 外形尺寸,例如 CEM、M.2、U.2 和 U.3,并且能够连接到当今可用的大多数 PCIe 设备。 除了显示眼图之外,TMT4综合测试仪还提供有关其接收器所使用的补偿的信息,以最大化眼图的高度和宽度。

该系统为发射机测试提供了两个重要的数据: 每个通道/预设组合的眼图,可以在容差测试仪接收器上进行测量。 容差测试仪的接收器训练值,用于完全打开眼图。

在接收端,可以对测试件的接收器路径进行功能评估。 具体来说,它旨在确定从容差测试仪发出的信号在返回超出预期操作范围的错误之前会衰减多少。

在这种使用场景中,新的TMT4 PCIE性能综合测试仪作为一个额外的设备,专注于传输和接收通道容差,允许用户在短短几分钟内评估PCIe Gen 3和PCIe Gen 4设备的运行情况。 情况成为可能。

发布日期: 2024-05-29

发布日期: 2023-11-24

发布日期: 2024-06-04

发布日期: 2024-11-27

发布日期: 2024-06-17

发布日期: 2024-05-09

发布日期: 2024-05-31

发布日期: 2024-07-17

发布日期: 2025-05-19

发布日期: 2025-05-19

发布日期: 2025-05-19

发布日期: 2025-05-19

发布日期: 2025-05-19

寻找更多销售、技术和解决方案的信息?

广州绿测电子科技有限公司(简称:绿测科技)成立于2015年11月,是一家专注于耕耘测试与测量行业的技术开发公司。绿测科技以“工程师的测试管家”的理念向广大客户提供专业的管家服务。绿测科技的研发部及工厂设立于广州番禺区,随着公司业务的发展,先后在广西南宁、深圳、广州南沙、香港等地设立了机构。绿测科技经过深耕测试与测量领域多年,组建了一支经验丰富的团队,可为广大客户提供品质过硬的产品及测试技术服务等支持。

技术工程师

020-22042442