DC-DC 转换器中的软开关可减少能量损耗。SiC 晶体管可实现更高的开关频率,因此磁性元件更小,从而减少热量。

效率和功率密度都是电源转换器设计中的重要因素。每个造成能量损失的因素都会产生热量,而这些热量需要通过昂贵且耗电的冷却系统来去除。软开关和碳化硅 (SiC) 技术的结合可以提高开关频率,从而可以减小临时存储能量的无源元件的尺寸和数量,并平滑开关模式转换器的输出。SiC 还为产生更少热量并利用更小散热器的转换器提供了基础。

对于传统的硅功率晶体管,电源转换器设计从简单的硬开关架构过渡到软开关,可以提高效率和频率。但是,我们可以利用 SiC 技术走得更远。工艺技术的改变使软开关的应用更加有效。

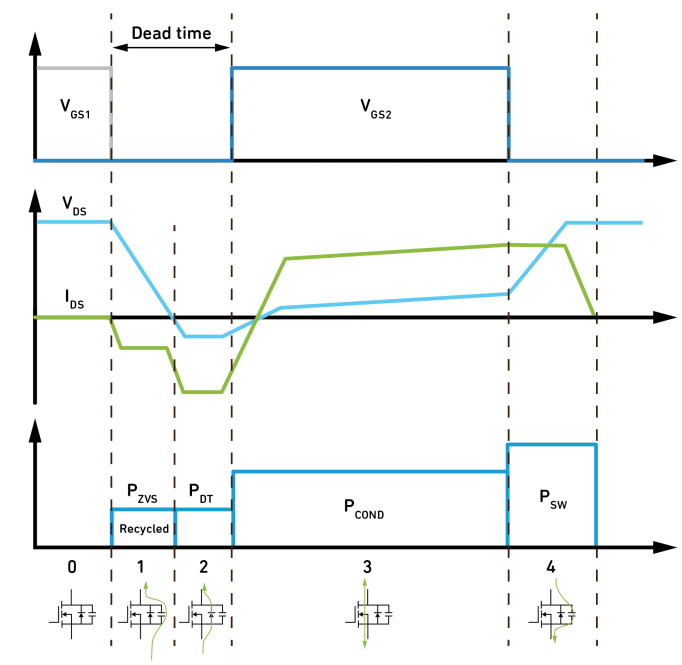

硬开关和软开关之间的主要区别在于,软开关可减少或消除功率晶体管开启和关闭阶段默认电压和电流条件的损耗贡献。图 1显示了这些不同阶段对损耗的贡献。

图 1. ZVS 软开关波形和半桥在开关的不同阶段的能量损失的主要来源。

设计人员已采用零电压开关 (ZVS) 技术与硅技术来消除开启开关损耗。电源开关中其余的主要损耗是传导损耗和关断开关损耗。随着开关频率的增加,电压和电流的同时摆动会导致相当大的损耗。从概念上讲,软开关可以调整电压和电流时序摆动以减少或消除损耗。术语“软开关”适用于设计人员可以用来限制损耗的多种技术。

零电压开关 (ZVS) 是开启阶段使用最广泛的软开关形式,其核心原理很简单:在电流自由流过晶体管通道之前降低漏极和源极之间的电压。开启前,输出电容充电至与V DS相同的水平。输出电容是漏极-源极电容与栅极和漏极之间电容的总和。要享受 ZVS 的好处,存储的电荷必须放电到负载中,以避免在开启期间漏极-源极电压同时下降和漏极-源极电流上升造成的损耗。理想情况下,电流开始上升时晶体管通道两端的电压已经很低(接近于零)。

其他损失来源

尽管 ZVS 的广泛使用解决了开关转换器中最重要的损耗源,但还有其他损耗源需要设计人员仔细注意,以便充分利用更高频率的操作。一些更传统的设计中的应用暴露了这些低效率。领先的 AI 应用(例如大型语言模型)的需求导致对接近 IC 封装热极限运行的加速器的需求增加,数百瓦的功率被传送到 PCB 上的每个设备。这导致为承载多核微处理器、图形处理单元和专用 AI 加速器的高密度机架供电所需的电力急剧增加。

电力需求已达到这样的程度:电源转换器需要为机架式系统提供高达 8 kW 的电力。在此过程中,它们将从几百伏特的交流或直流电源中获取电能,并在高电流水平下将电压降至 48 V,以分配给各个处理器组合体。这就要求电源转换器兼具高效率和高密度。转换器还需要承受 600 V 或更高电压浪涌故障。由于 ZVS 软开关将导通开关损耗降低到接近零,因此功率半导体的主要损耗变为 ZVS 软开关应用中的传导损耗。这将重点放在效率损失的下一个关键原因上:电流通过时晶体管通道中的电阻引起的传导损耗。

低阻力

理想情况下,电源转换器的导通电阻应尽可能低。工艺改进已帮助硅超结器件满足这些需求。然而,设计人员现在可以利用宽带隙技术(如碳化硅 (SiC)),从总线电压在 400V 至 800V 范围内的应用的较低电阻中获益。

SiC 在高密度电源转换器中的一大关键优势是,它能够以非常低的 R dsA(单位面积导通电阻)支持高击穿电压,这对于在数据中心部署而言是一个关键优势,因为数据中心的配电电压需要足够高,以防止通过电源线造成过大的电阻损失。

SiC 器件并非完全相同。为了利用效率和功率密度的改进,人们很容易将硅超结 MOSFET 替换为最接近的 SiC 等效器件。基于 SiC 的设计提供了其他机会,值得将 MOSFET 结构替换为可大幅降低导通电阻的结构。结型场效应晶体管 (JFET) 结构具有关键优势。它具有概念上更简单的结构,如图 2右下角所示。因此,它提供了较低的总电阻,这得益于载流子不必从源极通过类似 MOSFET 的通道,然后进入连接到漏极的 n 型漂移区。这使得导通电阻更接近由击穿电压控制的理论极限。与 MOSFET 相比,这使得 JFET 能够提供较高的击穿电压安全裕度,同时提供较低的单位面积导通电阻。

图 2. 该图比较了共源共栅电路中使用的 SiC MOSFET 和 SiC JFET 的横截面。

JFET 在电源电路中不太常用的一个原因是,它是一种常开器件,需要负电压才能完全关闭。共源共栅结构可实现更像 MOSFET(常闭)的控制。这使 SiC JFET 与低压硅 MOSFET 串联。通过在共源共栅配置中使用低压 Si 器件(如图 2 右上角所示),设计人员可以最大限度地降低总工作电阻。平衡设计可使 MOSFET 对总导通电阻的贡献不到 10%。可以将 MOSFET 和 JFET 集成在一个封装中,以帮助集成和设计 - 这种器件类型是 SiC FET,不同于 SiC MOSFET。

通过使用低压 Si MOSFET 将控制栅极与 JFET 分离,可以避免其他通常会降低基于 MOSFET 的设计性能的权衡。栅极控制的解耦使得可以优化栅极电压及其相关电荷,而不会牺牲 SiC 的性能。标准 SiC MOSFET 通常需要高栅极电压。这通常需要接近 20 V 才能保证在整个工作温度范围内正常运行。与 JFET 耦合的共源共栅架构可以使用较低的栅极电压(0 V 至 12 V)。这有助于减少栅极电荷,这是切换过程中产生的另一个潜在损耗源,尤其是对于轻负载下具有高开关频率的软开关应用。

在级联配置中同时使用 JFET 和硅 MOSFET 可通过降低米勒电容(栅极至漏极电容,C gd)进一步提高效率。高电容会对 MOSFET 的开关速度产生不利影响。级联配置带来的改进可延续到密度方面,因为它们可使开关频率高于传统硅器件的实际频率。

尽管 ZVS 避免了开启损耗,但仍存在死区时间,在此期间没有电力输送。对于基于硅的设计,这个死区时间可能长达 300 纳秒,它限制了最大可用开关频率,因为它减少了每个周期可用于导通状态的比例。在 500 kHz(2 µs 周期)的开关频率下,开启和关闭边缘的 300 纳秒死区时间占导通周期的 30%。与硅超结 MOSFET 相比,SiC JFET 的输出电容降低了 10 倍,从而大大缩短了所需的死区时间并提高了频率。

重要的是不要忽视关断阶段的损耗降低机会,这在改用 SiC 技术时可能更具优势。如果晶体管关断时不使用附加电路,电流和漏源电压将同时变化。这将导致类似于开通阶段硬开关的损耗。然而,快速关断不仅会降低关断开关损耗,还会在器件漏源端子上引入高关断电压尖峰和振铃。

有两种常用方法来控制关断漏极-源极电压尖峰和振铃。一种方法是使用高栅极电阻 ( R g ) 来减慢器件开关速度。另一种方法是使用低栅极电阻和漏极-源极 RC 缓冲器来抑制V DS尖峰和振铃。一个常见的误解是使用缓冲器效率非常低。对于通常采用 ZVS 开关技术的 LLC 谐振或相移全桥等拓扑,使用缓冲器比使用高栅极电阻更有效。

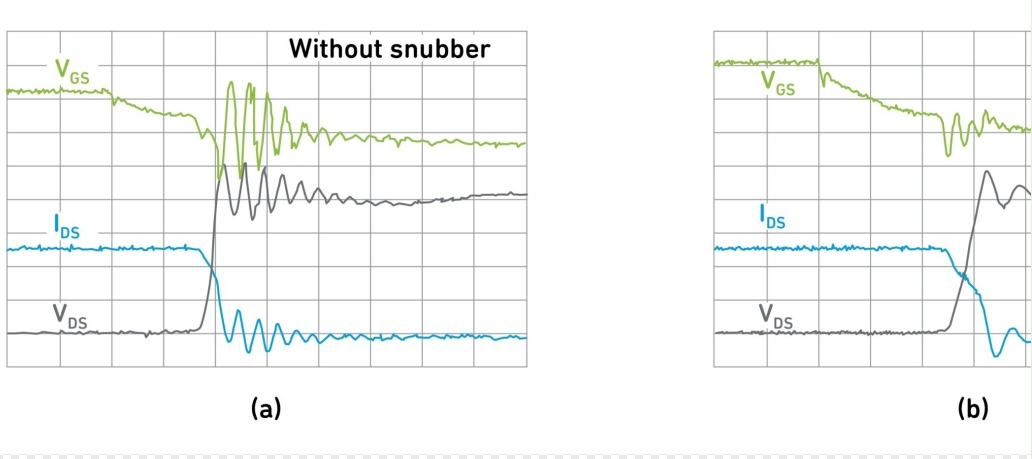

在 ZVS 软开关应用中,添加的漏极至源极缓冲电容器不会产生任何导通损耗。漏极和源极之间的额外缓冲电容与低栅极电阻相结合,在关断 d V /d t转换期间在互补续流器件中提供更高的位移电流。这可以进一步减少关断电流和电压之间的重叠,与仅使用高栅极电阻相比,可大大降低关断开关损耗。通过这种方法,我们可以控制V DS振铃,而不会牺牲器件开关速度,而如果要使用高栅极电阻策略,则需要牺牲器件开关速度。图 3显示了如何使用缓冲器来减少振铃。

图 3. E1B 封装 SiC 模块的 VDS 800 V IDS 100 A 关断波形显示了使用缓冲电容器和不使用缓冲电容器之间的差异。

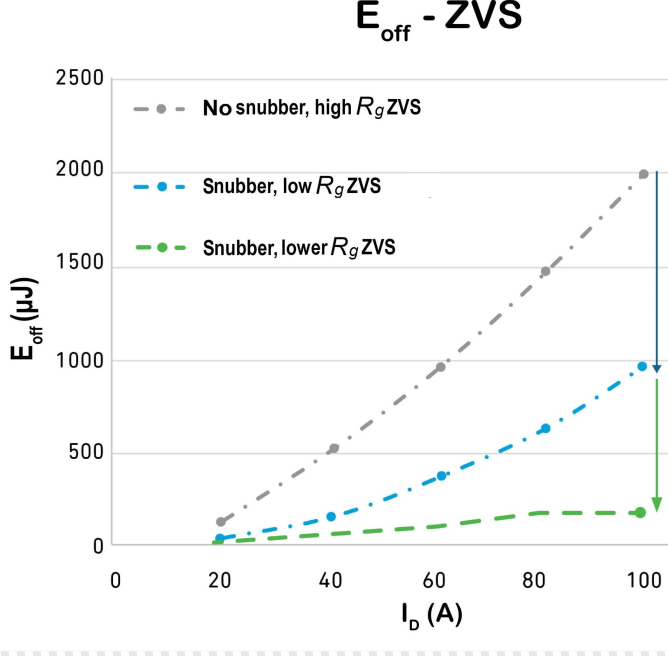

图 4中,使用 800 V 总线电压和 100 A 负载电流进行的双脉冲测试表明,添加缓冲器可使 SiC MOSFET 模块的损耗减少 52%。将基于 JFET 的器件与缓冲器结合使用,可将关断开关损耗额外减少 74%。这使得开关速率可以提高三倍,并推动外部无源元件尺寸的减小。引用 50 kW 相移全桥 (PSFB) 的模拟,关断开关损耗减少 74% 可使结温降低 10%。最终,更好的热性能可使散热器和冷却结构更小;两者结合起来,可减少转换器体积。

图 4. E1B 封装 SiC 模块在 VDS 800 V、IDS 100 A 条件下的关断开关损耗双脉冲测试结果。图表显示了降低 Rg 和使用缓冲器来降低模块能耗的效果。

尽管软开关有许多复杂之处,但 SiC 技术提供了优化其使用的机会。需要高效率和高密度的设计可以通过突破传统 MOSFET 结构的限制来实现其目标。

发布日期: 2024-09-30

发布日期: 2024-06-07

发布日期: 2024-06-18

发布日期: 2023-12-19

发布日期: 2023-12-05

发布日期: 2024-05-13

发布日期: 2024-05-08

发布日期: 2024-11-29

发布日期: 2025-04-24

发布日期: 2025-04-24

发布日期: 2025-04-24

发布日期: 2025-04-24

发布日期: 2025-04-24

寻找更多销售、技术和解决方案的信息?

广州绿测电子科技有限公司(简称:绿测科技)成立于2015年11月,是一家专注于耕耘测试与测量行业的技术开发公司。绿测科技以“工程师的测试管家”的理念向广大客户提供专业的管家服务。绿测科技的研发部及工厂设立于广州番禺区,随着公司业务的发展,先后在广西南宁、深圳、广州南沙、香港等地设立了机构。绿测科技经过深耕测试与测量领域多年,组建了一支经验丰富的团队,可为广大客户提供品质过硬的产品及测试技术服务等支持。

技术工程师

020-22042442