新闻资讯

作为收发射频(RF)信号的无源器件,天线决定了通信质量、信号功率、信号带宽、连接速度等通信指标,是通信系统的核心。为了进一步提升移动通信系统的容量,采用毫米波频率进行定向通信的技术是5G预期配置的关键技术之一,通信频段由6GHz以下(Sub-6GHz)提升至毫米波频段(24GHz以上),从而通过更大的通信带宽来提升通信系统的容量。

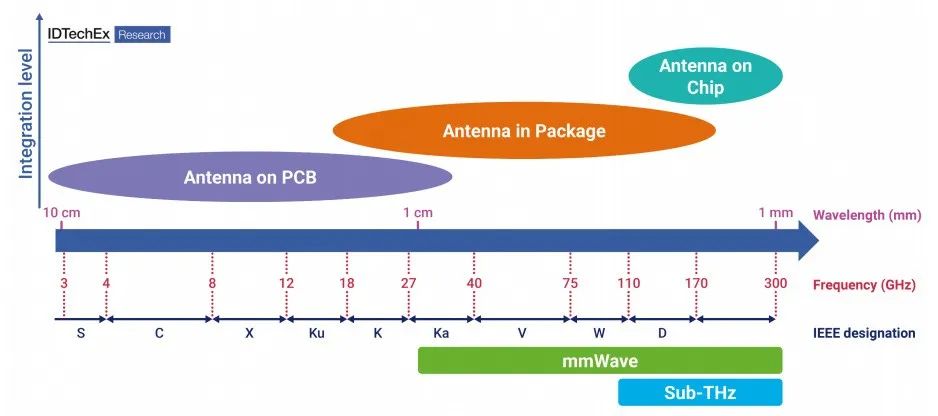

如何实现毫米波天线阵列,有两种常见方式:AoC(Antenna on Chip)、AiP(Antenna in Package)。

AiP技术在5G市场中胜出

更高频率的信号就意味着更大的馈线损耗,根据测算,传统4G手机射频前端的馈线损耗只有1dB不到,但是在毫米波频段线损在2-4dB,损耗比低频率波大。由于毫米波馈线损耗大,毫米波天线不能再作为分立器件单独设计。因此,5G时代将天线与射频前端进一步集成就成为大势所趋,保持辐射效率的同时缩小天线尺寸成为一项具有挑战性的任务。

而这一集成趋势在宏基站侧就体现为基于Massive MIMO的AAU,在室分基站侧就体现为由DAS向数字化室分的演进,在终端侧就体现为AiP的诞生。

AoC技术于缩减天线尺寸上的效能极佳,但需经由半导体材料与制程上的统一,并与其他元件一同结合于单一芯片中,考量制造成本与芯片特性,AoC较适合应用于太赫兹(Terahertz)频段中,因此在频段使用与成本等因素上,其竞争力并不在毫米波频段。

由于射频元件大多使用GaAs为基底材料、天线多使用LCP(Liquid Crystal Polymer)为材料等,因而较适合应用于SiP技术,使得封装天线AiP技术逐渐胜出。现阶段各家芯片设计大厂(如Qualcomm)、射频元件商(如Skyworks、Qorvo)及封测代工厂(如日月光、Amkor)等,大多选择以AiP技术为研发方向切入5G通讯市场。

天线封装技术与工作频率

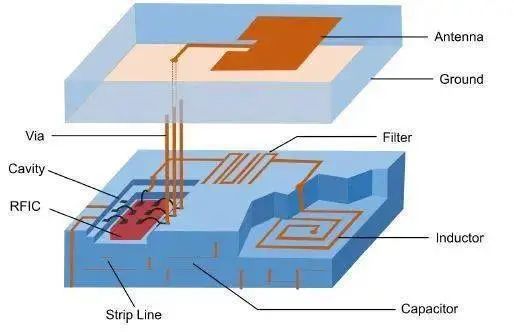

AiP技术可以说是5G毫米波频段毫米波终端天线最适合的方案,基于封装材料与工艺将天线、射频收发器、射频前端集成以及电源管理芯片集成在一起上,实现系统级无线通信模组,以减少射频馈线带来的损耗,实现更大的有效辐射功率。AiP技术兼顾了天线的性能、成本和体积,并具有高集成度的优势,代表着近年来天线技术的重大成就及5G毫米波频段终端天线的技术升级方向。

CMOS工艺把射频芯片和数字芯片集成到一起变成SoC这一步本身就是很大的突破,SoC芯片的问世,不仅大大降低了客户产品的开发难度,且整个系统成本也随之下降。那么到底能下降多少成本呢?从第一代的砷化镓到锗硅,整个系统成本大概降了50%;到了CMOS工艺的时代,跟上一代锗硅相比又降了40%的系统成本;而到SoC时代,又会带来30%的成本降低。在此之上如果把天线集成到系统形成一颗AiP的SoC芯片,整个系统成本能够进一步下探约25%,降本效果是非常明显的。

天线尺寸与电磁波波长成正比,客观上毫米波天线的尺寸要比低频率天线小很多,除了手持和其他小型毫米波设备所需的小尺寸,AiP技术还能提高信号完整性,减少信号衰减,并克服高频率所带来的范围和传输挑战。

在从700MHz过渡到4G LTE的3.5GHz,再到5G的6-60GHz的过程当中,RF开关和频带复杂性以及天线设计和调试复杂性(从8x8 MIMO到68x4 MIMO)的增加是随之出现的其中一些变化。AiP技术实现了5G所承诺的改进,在封装层面克服很多技术挑战。

可以说毫米波天线集成技术是实现毫米波高分辨数据流、移动分布式计算等应用场景的关键技术。AiP技术具有广泛的应用,如2.4GHz的物联网,60GHz的虚拟现实、增强现实和手势识别,以及79GHz的汽车雷达。然而,AiP技术真正具有突破性的应用是在28GHz和39GHz的5G NR智能手机方面。综上所述,AiP技术不再是一种选择性技术,而是无线SoC的必选技术,将用于所有基于5G毫米波的基站和支持5G的电子产品。

5G正在全球范围内逐步商业化,虽然截至目前,只有不到10%的商业化或预商业化5G服务基于毫米波频段,主要部署仍然是中频(Sub-6GHz)。但是IDTechEx在《2024-2034年5G和6G封装天线(AiP):技术、趋势和市场》中预测,2023年到2034年,应用于5G毫米波的AiP复合年增长率将达40.7%。在毫米波应用大放异彩的今天,AiP技术优化了毫米波性能,给予了毫米波充裕的设计灵活性,也将毫米波推向更多的应用领域。

AiP技术演进之路

AiP早期与蓝牙无线技术一起发芽,由于其继承发扬了微带天线、多芯片电路模块、瓦片式相控阵结构的集成概念,驱动了研究者自90年代末不断深入探索在芯片封装上集成单个或多个天线,这一阶段的研究工作主要集中在大学实验室,如何实现天线小型化是研究者所面临的主要问题。

到了中期,AiP与60GHz无线技术及毫米波雷达一起成长:2010年IBM便公布了用于60GHz相控阵系统的完整AiP方案,该方案基于LTCC工艺将16个矩形微带天线集成在BGA封装中,发射或接收裸芯片通过倒装焊技术与AiP相连,之后IBM进一步将其AiP的工作频段推进到94GHz;2011年、2012年三星、Intel则分别发布了用于60GHz的相控阵系统AiP方案,同样基于LTCC与BGA工艺;2015年谷歌首次推出了使用60GHz信号快速追踪人手移动的手势雷达。如今几乎所有的60GHz无线通信和手势雷达芯片都采用了AiP技术。

典型的AiP天线结构

AiP工艺主要有LTCC(低温共烧结陶瓷)、HDI(高密度互联)及FOWLP(晶圆级扇出式封装)三种方案。基于更高的集成度、更好的散热性、更低的传输损耗等优势,并结合目前的产业化进度,FOWLP有望成为AiP天线的主流技术工艺。

FOWLP工艺不同于LTCC或HDI工艺,FOWLP不再需要叠层基片,转而用模塑化合物、重新配置金属与介质层代替,基于FOWLP的AiP是由英飞凌公司研发的eWLB(嵌入式晶圆级封装)工艺发展而来。

eWLB是将裸芯片嵌入在厚度为470μm的模塑化合物中。在裸芯片的扇入区以及封装的扇出区涂有介质层D1起到保护裸芯片的作用,D1层的厚度通常为6.5μm。重新配置的导体层(RDL)是沉积厚度为7.5μm的铜,用于实现连接线或天线。

由于eWLB工艺仅有一层金属,不利于实现基于FOWLP的AiP。为此,台积电开发出InFO-AiP技术,通过在模塑化合物上增加一层金属,微带天线辐射片由模塑化合物上面增加的金属层实现,微带天线地、馈线及耦合槽则在RDL金属层实现。

FOWLP是fan-out Wafer Level Package的缩写,其中WLP(晶圆级封装)是以BGA(Ball Grid Array)技术为基础,以wafer为加工对象,在wafer上同时对众多芯片进行封装测试,最后切割成单个器件,可直接贴装到基板或者PCB板上的封装方案。WLP由于不需要中介层(interposer)、填充物(underfill)与导线架,并且省略黏晶、打线等制程,因此能够大幅减少材料及人工成本,此外,WLP大多采用RDL(重布线层)与Bumping(凸块)技术作为I/O排线手段,因此具有较小的封装尺寸和较佳电性表现等优势,多应用于注重轻薄、节能的3C芯片中。

WLP可分为fan-in(标准型扇入式)及fan-out(扩散性扇出式)两种,其中fan-in是在wafer未进行切片前对wafer进行封装,之后再进行切片分割,完成后的封装大小和芯片尺寸接近。而fan-out则是基于wafer重构技术,将芯片重新布局到一块人工晶圆上,然后按照与标准的WLP工艺类似的步骤进行封装,封装面积大于芯片面积。传统的WLP封装多采用fan-in形态,应用于pin(引脚)数量较少的IC芯片,伴随着IC引脚数目的增加,对锡球间距的要求日趋严格,加上PCB排线对于IC封装后尺寸以及引脚位置的调整要求,因此衍生出fan-out。

值得注意的是,由于波长短,电路尺寸小,加工精度极其重要,传统技术难以保证AiP模组加工精度上的一致性。采用AME技术的电路板可以实现较高的加工精度,将磁介质厚度精度控制在50um之内,金属走线精度控制在30-40um之内,满足对加工精度的需求。另外,AME技术可实现几乎无限制的空间结构,可实现传统制造技术无法实现的特殊电路结构、复杂空间构造,材料结构特性可控、加工过程可视化。可实现不同种类的基材以各种形式进行复合、堆叠,满足对高集成度、多功能AiP实现的需求,简化了传统制板加工流程,降低了制造成本。

发布日期: 2026-01-27

发布日期: 2026-02-06

发布日期: 2024-06-17

发布日期: 2024-05-06

发布日期: 2024-04-11

发布日期: 2024-02-26

发布日期: 2024-05-16

发布日期: 2024-04-23

发布日期: 2026-04-07

发布日期: 2026-04-07

发布日期: 2026-04-07

发布日期: 2026-04-07

发布日期: 2026-04-03